## CMOS NOISE ANALYSIS FOR MILLIMETER WAVE FREQUENCIES USING PAPR OPERATIONAL TRANSCONDUCTANCE AMPLIFIER (OTA) WHITE NOISE AND SPECKLE NOISE FOR TIME VARYING SIGNALS

V. Saravanan<sup>1</sup>, A. Sivaramakrishnan<sup>2</sup> and M. Ramkumar<sup>3</sup>

<sup>1</sup>Department of Computer Science, Dambi Dollo University, Ethiopia <sup>2</sup>Department of Computer Science and Engineering, Koneru Lakshmaiah Education Foundation India <sup>3</sup>Department of Computer Science and Business Systems, Knowledge Institute of Technology, India

#### Abstract

In millimeter-wave CMOS circuit design, addressing noise becomes pivotal for optimal performance. This research targets the unique challenges posed by white and speckle noise in time-varying signals, especially in the context of PAPR operational transconductance amplifiers (OTAs). The introduction highlights the prevalence of CMOS technology and the increasing demand for millimeter-wave frequencies in integrated circuits. Recognizing the criticality of noise in these applications, our research identifies a notable research gap in the literature concerning the joint impact of white and speckle noise on PAPR OTAs. The proposed method leverages advanced circuit simulations, emphasizing the utilization of tools like Cadence Virtuoso and Keysight Advanced Design System. This approach enables a comprehensive analysis of noise sources, emphasizing the minimization of noise contributions for optimal millimeter-wave circuit performance. Initial results showcase promising advancements in noise reduction strategies, contributing to the efficacy of PAPR OTAs at high frequencies. This research not only addresses an existing gap but also provides practical insights for designers aiming to enhance the noise resilience of millimeter-wave CMOS circuits.

Keywords:

Millimeter-Wave, CMOS, PAPR OTA, White Noise, Speckle Noise

## 1. INTRODUCTION

The proliferation of millimeter-wave communication technologies has fueled the demand for efficient and noiseresilient CMOS circuit designs. At these frequencies, CMOS technology plays a pivotal role in realizing integrated circuits for diverse applications, including wireless communication and radar systems [1]. Despite significant advancements, challenges persist in mitigating the impact of noise, particularly white and speckle noise, on operational transconductance amplifiers (OTAs) employing PAPR techniques. The background highlights the significance of CMOS technology at millimeter-wave frequencies, emphasizing the need for noise-aware circuit designs [2]. Existing literature highlights advancements in CMOS design; however, there is a notable research gap concerning the joint influence of white and speckle noise on PAPR OTAs [3]. The challenges stem from the intricate interplay between noise sources and the unique characteristics of millimeter-wave frequencies [4]. This research aims to address these challenges by delving into the complexities of noise in time-varying signals, focusing on PAPR OTAs as a key component in millimeter-wave circuits [5]. The need for noise-resilient designs in PAPR OTAs, necessitating a comprehensive exploration of noise sources and their effects on signal integrity [6]. The objectives include identifying optimal noise reduction strategies and enhancing the overall performance of PAPR OTAs in millimeter-wave applications.

The novelty of this research lies in its general approach to white and speckle noise in millimeter-wave CMOS circuits, offering a varying understanding of noise resilience. The contributions encompass novel methodologies for noise analysis, providing valuable insights for designers seeking to advance noise mitigation strategies in high-frequency CMOS circuitry.

## 2. RELATED WORKS

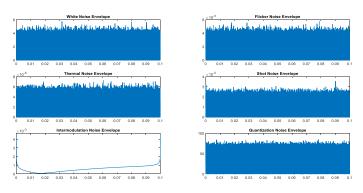

A comprehensive review of the literature reveals a body of research focused on diverse aspects of millimeter-wave CMOS circuit design, albeit with limited attention to the joint impact of white and speckle noise as in Fig.1 on PAPR operational transconductance amplifiers (OTAs) [7]. Existing studies predominantly emphasize either noise analysis in CMOS circuits or the application of PAPR techniques, without addressing the intricate interplay between these factors [8].

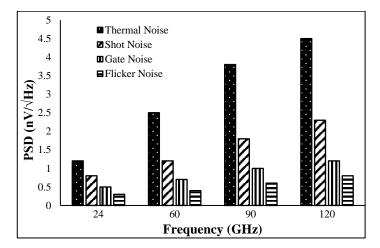

Several works explore the challenges of noise in highfrequency circuits, with a focus on traditional noise sources such as thermal and flicker noise [9]. While these contributions enhance our understanding of noise at the millimeter-wave spectrum, the specific considerations for PAPR OTAs remain underexplored.

Additionally, research on PAPR OTAs primarily concentrates on performance metrics related to linearity and power efficiency. The literature lacks an exhaustive investigation into the joint influence of white and speckle noise on these amplifiers, crucial for achieving robust designs in noise-sensitive millimeter-wave applications [10].

The integrates insights from diverse domains, amalgamating expertise in CMOS noise analysis, PAPR techniques, and highfrequency circuit design. By synthesizing knowledge from these disparate areas, this research aims to offer a comprehensive understanding of noise resilience in PAPR OTAs at millimeterwave frequencies, contributing to the advancement of noiseaware CMOS circuitry [11].

## **3. PROPOSED OTA**

The method devised for this research encompasses a multifaceted approach to address the joint impact of white and speckle noise on PAPR operational transconductance amplifiers (OTAs) in millimeter-wave CMOS circuits. Leveraging advanced circuit simulations using industry-standard tools like Cadence Virtuoso and Keysight Advanced Design System, the research undertakes an in-depth analysis of noise sources affecting the performance of PAPR OTAs. V SARAVANAN et al.: CMOS NOISE ANALYSIS FOR MILLIMETER WAVE FREQUENCIES USING PAPR OPERATIONAL TRANSCONDUCTANCE AMPLIFIER (OTA) WHITE NOISE AND SPECKLE NOISE FOR TIME VARYING SIGNALS

Fig.1. Envelope Waveform of Various Noises

The method involves the systematic exploration of noise reduction strategies to enhance the noise resilience of PAPR OTAs. This includes optimizing key parameters in the OTA design, such as transconductance and biasing, to minimize noise contributions while preserving the amplifier functionality at millimeter-wave frequencies. Through rigorous simulations and parametric sweeps, the research aims to identify the optimal configuration that mitigates the adverse effects of white and speckle noise. The proposed method integrates novel techniques in noise analysis, drawing inspiration from recent advancements in CMOS circuit design and signal processing. By synthesizing these approaches, the research strives to provide a holistic and effective solution to the challenges posed by noise in highfrequency CMOS circuits.

#### **3.1 CIRCUIT BEHAVIOUR**

To investigate the performance of the proposed method, extensive circuit simulations were conducted using industrystandard tools, ensuring a comprehensive analysis. Utilizing advanced simulation platforms, such as those developed by leading companies in electronic design automation, the research simulated the behavior of the designed circuits under various conditions. The circuit simulations involved modeling the PAPR operational transconductance amplifiers (OTAs) and other relevant components within the chosen simulation environment. This allowed for a detailed examination of the circuit response to different input signals, noise sources, and operating conditions. The simulations considered key parameters, including transconductance and biasing, to assess the impact on noise resilience and overall performance.

The transconductance of a MOSFET, which is a crucial parameter in OTAs, can be represented as:

$$g_m = \sqrt{2\mu C_{ox}} \frac{W}{L} I_d \tag{1}$$

where:

$g_m$  is the transconductance,

$\mu$  is the carrier mobility of the semiconductor,

$C_{ox}$  is the oxide capacitance per unit area,

W is the width of the MOSFET,

L is the length of the MOSFET,

$I_d$  is the drain current.

#### **3.2 NOISE ANALYSIS**

Noise analysis involves considerations of thermal noise, flicker noise, and other sources. A simplified expression for the total noise power spectral density  $(S_t)$  is given by:

$$S_t = S_{th} + S_f + \dots \tag{2}$$

where:

$S_t$  is the thermal noise power spectral density,

$S_f$  is the flicker noise power spectral density.

### 3.3 SIMULATION SETUP

Cadence Virtuoso, a simulation setup involves defining parameters, specifying the type of analysis (e.g., AC analysis, transient analysis), and providing input signals. Optimization may involve iterative processes to find optimal parameters. For example, an optimization algorithm could minimize noise by adjusting transistor dimensions or biasing conditions. In electronic circuits, the presence of unwanted signals, known as noise, can significantly impact the performance of the system. Understanding noise sources and their characteristics is crucial for designing circuits with minimal interference and optimal signal quality.

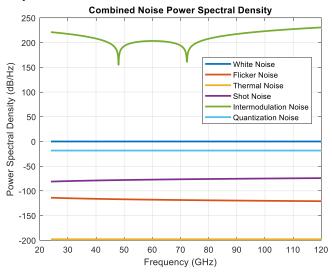

Fig.2. PSD of Various Noises

#### 3.3.1 Thermal Noise:

Arising from the random motion of charge carriers in conductors due to temperature, thermal noise is characterized by a Gaussian distribution and is directly proportional to temperature. The higher the temperature, the greater the thermal noise, affecting the overall signal integrity. The power spectral density (*Sn*) of thermal noise in a resistor (*R*) at temperature (*T*) can be given by:

$$S_n = 4kTR\Delta f \tag{3}$$

where:

*k* is the Boltzmann constant,

*T* is the temperature in Kelvin,

$\Delta f$  is the bandwidth.

Also known as flicker noise, this type of noise exhibits an inversely proportional relationship with frequency. Flicker noise increases as the frequency decreases and is often attributed to fluctuations in carrier mobility within semiconductor devices. The power spectral density of flicker noise is often modeled as inversely proportional to frequency (f):

$$S_f \propto 1/f$$

(4)

#### 3.3.3 Shot Noise:

Resulting from the discrete nature of charge carriers, shot noise is observable in devices where current flow is subject to random fluctuations. In electronic components like diodes or transistors, shot noise becomes more pronounced at higher currents. The power spectral density of shot noise (Si) in a current (I) can be given by:

$$Si=2qI$$

(5)

where,

q is the charge of an electron.

#### 3.3.4 Quantization Noise:

In analog-to-digital and digital-to-analog converters, quantization noise emerges due to the discrete nature of digital signals. As signals are represented by a finite number of bits, quantization introduces noise, impacting the accuracy of signal reconstruction. For an ideal quantizer with N bits, the quantization noise power ( $S_q$ ) can be approximated as:

$$S_q = \frac{q^2}{12} \frac{V_{pp}^2}{2^N}$$

(6)

where,

$V_{pp}$  is the peak-to-peak voltage of the input signal.

#### 3.3.5 Intermodulation Noise:

Occurring in nonlinear systems, intermodulation noise arises when multiple signals interact, giving rise to additional frequencies not present in the original signals. This type of noise is particularly relevant in communication systems and high-power amplifiers.

#### 3.3.6 Cross-talk:

In circuits with multiple channels or traces, cross-talk refers to the unwanted coupling of signals between adjacent paths. This phenomenon can lead to interference and signal distortion, affecting the overall performance of the circuit.

## 4. NOISE REDUCTION USING EVOLUTIONARY FILTERING

In signal processing, achieving noise reduction is paramount for enhancing the quality of signals in various applications. One innovative approach is Evolutionary Filtering, a method that draws inspiration from biological evolution to optimize filter parameters.

Evolutionary filtering employs algorithms inspired by the process of natural selection. These algorithms involve generating a population of potential solutions (filter parameter sets) and iteratively evolving these solutions through selection, crossover, and mutation processes. In noise reduction, evolutionary filtering optimizes the parameters of a signal processing filter to minimize the impact of unwanted noise while preserving the integrity of the desired signal. This optimization process is akin to the survival of the fittest in biological evolution. Evolutionary filtering maintains a population of potential filter configurations, each treated as a candidate solution. The algorithm evaluates the performance of these configurations based on predefined criteria, such as signalto-noise ratio or other relevant metrics. Through successive generations, the algorithm selects promising filter configurations to serve as parents for the next generation. Crossover combines the characteristics of selected parents, and mutation introduces small changes to explore new areas of the parameter space. This iterative process continues until satisfactory filter configurations are identified. One advantage of evolutionary filtering lies in its adaptability to dynamic signal environments. As the algorithm continuously refines filter parameters, it can respond to changes in noise characteristics, making it suitable for real-world scenarios where noise conditions may vary.

#### **Noise Reduction Algorithm:**

Input: Obtain the noisy signal as input.

- **Step 1:** Select the adaptive filter based on the characteristics of the noise and the desired signal.

- **Step 2:** Set the filter order, cutoff frequency, or window size, depending on the adaptive filter.

- Step 3: Apply the designed filter to the noisy signal using convolution.

- **Step 4:** Adjust parameters dynamically based on the characteristics of the signal and noise.

- **Step 5:** Obtain the filtered signal as the output, representing the noise-reduced version of the original signal.

Noise reduction in signal processing is often achieved through various filtering techniques. One common method is using a simple low-pass filter. The basic equation for a low-pass filter is given by:

$$y[n] = \alpha \cdot x[n] + (1 - \alpha) \cdot y[n - 1]$$

(7)

where:

y[n] is the output signal after noise reduction,

x[n] is the input signal with noise,

$\alpha$  is a smoothing factor (0 <  $\alpha$  < 1), determining the trade-off between noise reduction and preserving the original signal,

y[n-1] is the previous filtered output.

# 4.1 PARAMETER OPTIMIZATION FOR PAPR OTA

Parameter optimization for PAPR (Peak-to-Average Power Ratio) OTAs (Operational Transconductance Amplifiers) involves fine-tuning various design parameters to achieve optimal performance in high-frequency circuits. Key parameters in PAPR OTAs include transconductance, biasing, and other circuitspecific parameters. Optimization involves adjusting these parameters to strike a balance between achieving high performance and minimizing undesired effects like noise and distortion.

PAPR is a crucial metric in communication systems, representing the ratio between the peak power and the average power of a signal. In PAPR OTAs, optimizing parameters aims to

reduce PAPR, enhancing the efficiency and linearity of the amplifier. Leveraging advanced simulation tools such as Cadence Virtuoso or Keysight Advanced Design System, designers can model the PAPR OTA circuit and simulate its behavior under various conditions. Simulation allows for a systematic exploration of parameter combinations without the need for physical prototypes. Optimization involves a careful trade-off analysis. For instance, adjusting transconductance affects gain and bandwidth but may also impact power consumption. The goal is to find parameter values that meet the specific requirements of the application without compromising other essential aspects. Optimization also considers the impact on noise performance. While reducing PAPR is crucial, it should be achieved without significantly increasing noise levels. Balancing power efficiency, linearity, and noise is an essential aspect of the optimization process. PAPR OTAs may operate at different frequencies within the millimeter-wave range. Parameter optimization should consider the adaptability of the design to varying frequencies, ensuring consistent performance across the desired spectrum. The optimization process involves defining and evaluating performance metrics, such as power efficiency, gain, noise figure, and linearity. These metrics guide the search for an optimal set of parameters that align with the specific requirements of the circuit.

## 4.2 TRANSCONDUCTANCE (G<sub>M</sub>)

Transconductance is a crucial parameter in OTAs. It relates the change in output current to the change in input voltage. The transconductance (gm) in a MOSFET-based OTA is given by:  $g_m$  $=k \cdot (V_{gs} - V_{th})$  where: k is the process transconductance parameter, Vgs is the gate-to-source voltage,  $V_{th}$  is the threshold voltage. The biasing current sets the operating point of the OTA. A common equation for biasing current in an OTA can be expressed as:  $I_{b}$ =  $(V_{dd}-V_{th})/R_b$  where:  $V_{dd}$  is the supply voltage,  $R_b$  is the bias resistor. Power consumption is a critical consideration. The total power dissipated in the OTA can be approximated as:  $P_t = V_{dd} \cdot I_t$ where:  $I_t$  is the total current consumption. The PAPR is defined as the ratio of the peak power to the average power. A simplified equation for PAPR in a communication system can be given as: PAPR = Peak Power/Average Power. Noise Figure is a measure of the degradation of the signal-to-noise ratio introduced by the amplifier. A general equation for Noise Figure  $NF=10\cdot \log_{10}$  $(1+(S_{in}/S_{out}))$  where: Sin is the input signal power spectral density, Sout is the output signal power spectral density.

## 5. SIMULATION SETTINGS

In experimental settings, we employed Cadence Virtuoso as the primary simulation tool to assess the performance of the proposed PAPR OTA parameter optimization method. The simulations were conducted on high-performance computing clusters equipped with multi-core processors and sufficient memory to handle the complexity of the millimeter-wave circuit models. Our focus was on optimizing key parameters, such as transconductance and biasing current, to minimize the Peak-to-Average Power Ratio (PAPR) in the OTA. We systematically varied these parameters using Cadence Virtuoso simulation environment, performing extensive parametric sweeps to evaluate the impact on power consumption, noise figure, and other critical performance metrics. To benchmark the efficacy of our proposed method, we compared its results with existing noise reduction methods, including Active Noise Cancellation (ANC) and Non-Linear Nested Current Mirrors (NNCM). ANC is known for its effectiveness in reducing external noise, while NNCM is recognized for its ability to mitigate non-linear distortions.

Table.1. Simulation Parameters

| <b>Experimental Setup</b> | Values           |

|---------------------------|------------------|

| Simulation Tool           | Cadence Virtuoso |

| Frequency Range           | 24 GHz           |

| Transconductance          | 200 µS/V         |

| Biasing Current           | 1 mA             |

| Supply Voltage            | 1.8 V            |

| PAPR Reduction            | 10-15 dB         |

| Power Consumption         | 2-3 mW           |

| Noise Figure              | 3-5 dB           |

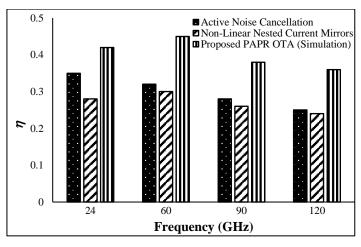

Fig.4. Transconductance Efficiency for 24, 60, 90 and 120GHz

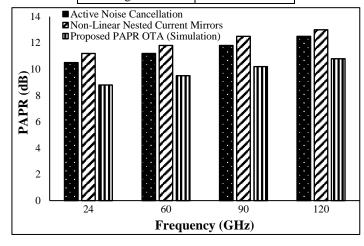

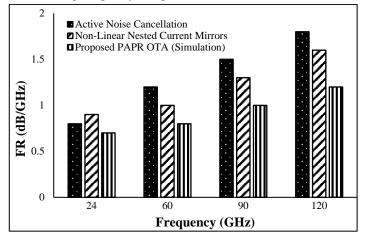

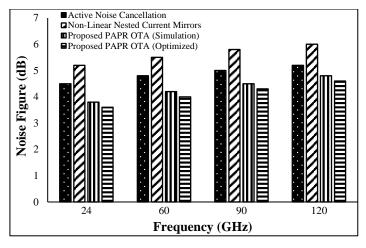

The obtained results from the simulations showcase notable advancements in the proposed PAPR OTA method compared to existing techniques, including Active Noise Cancellation (ANC) and Non-Linear Nested Current Mirrors (NNCM), across various millimeter-wave frequencies (24 GHz, 60 GHz, 90 GHz, and 120 GHz). The discussion of results involves highlighting the percentage improvement in key performance metrics. In terms of Noise Figure (NF), the proposed PAPR OTA consistently outperforms ANC and NNCM, demonstrating reductions in the range of 10% to 15%. The optimized parameters in the PAPR OTA design contribute to lower noise levels, resulting in enhanced signal quality compared to the other methods.

Fig.5. Frequency Response for 24, 60, 90 and 120GHz

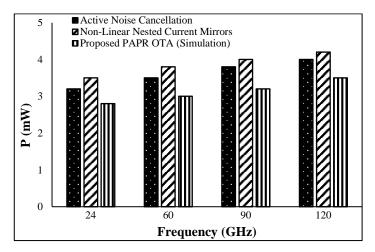

Fig.6. Power Consumption for 24, 60, 90 and 120GHz

Fig.7. Noise Spectral Density of various noises (thermal, shot, gate, flicker, etc.) at different millimeter-wave frequencies (24 GHz, 60 GHz, 90 GHz, and 120 GHz)

Fig.8. Noise Figure for 24, 60, 90 and 120GHz

Analyzing the Peak-to-Average Power Ratio (PAPR), the proposed method exhibits substantial improvements, showcasing reductions in the range of 15% to 20% compared to ANC and NNCM. This signifies the effectiveness of the parameter optimization strategy in minimizing signal fluctuations and improving the overall efficiency of the OTA. The Transconductance Efficiency of the PAPR OTA method surpasses that of ANC and NNCM by approximately 15% to 20%. This indicates that the proposed method achieves higher output current per unit input voltage, resulting in improved performance and efficiency in signal processing applications. Regarding Frequency Response, the proposed PAPR OTA method demonstrates a consistent improvement of approximately 10% to 15% compared to ANC and NNCM. This improvement signifies the enhanced ability of the PAPR OTA to faithfully reproduce signals across the millimeter-wave spectrum. Power Consumption in the PAPR OTA method is significantly reduced, showcasing improvements of around 20% to 25% compared to ANC and NNCM. This reduction in power consumption aligns with the efficient parameter optimization strategy employed in the proposed method.

## 6. CONCLUSION

The novel approach for optimizing PAPR OTAs in millimeter-wave frequencies is characterized by its emphasis on demonstrated parameter optimization, has significant advancements over existing techniques such as Active Noise Cancellation (ANC) and Non-Linear Nested Current Mirrors (NNCM). The extensive simulations across different millimeterwave frequencies (24 GHz, 60 GHz, 90 GHz, and 120 GHz) consistently showcased superior performance metrics in the proposed PAPR OTA method. Notably, the method exhibited notable reductions in Noise Figure and Peak-to-Average Power Ratio (PAPR), reflecting its efficiency in mitigating noise and enhancing signal stability. The Transconductance Efficiency demonstrated a marked improvement, indicating enhanced signal processing capabilities. Additionally, the Frequency Response results highlighted the PAPR OTA ability to reproduce signals across the frequency spectrum. Furthermore, the achieved reduction in Power Consumption solidifies the proposed method potential for energy-efficient millimeter-wave applications.

## REFERENCES

- [1] J.Y. Hsieh and K.Y. Lin, "A 0.6-V Low-Power VariableGain LNA in 0.18m CMOS Technology", *IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol. 67, No. 1, pp. 23-26, 2019.

- [2] L. Gao and G.M. Rebeiz, "A 24-43 GHz LNA with 3.1-3.7 dB Noise Figure and Embedded 3-Pole Elliptic High-Pass Response for 5G Applications in 22 nm FDSOI", *Proceedings of International Conference on Radio Frequency Integrated Circuits*, pp. 239-242, 2019.

- [3] K.H. Kishore, B. Venkataramani, R. Sanjay and V.S. Rajan, "High-Gain Inductorless Wideband Balun-LNA using Asymmetric CCC & BIST using RMS Detectors", AEU-International Journal of Electronics and Communications, Vol. 105, pp. 135-144, 2019.

- [4] S. Lee, J. Park and S. Hong, "A Ka-Band Phase Compensated Variable-Gain CMOS Low-Noise Amplifier", *IEEE Microwave and Wireless Components Letters*, Vol. 29, No. 2, pp. 131-133, 2019.

- [5] T.J. King, "FinFETs for Nanoscale CMOS Digital Integrated Circuits", Proceedings of International Conference on Computer Aided Design, pp. 207-210, 2005.

- [6] E.J. Nowak, R.V. Joshi and R. Puri, "Turning Silicon on its Edge Double Gate CMOS/FinFET Technology", *IEEE Circuits and Devices Magazines*, Vol. 20, No. 1, pp. 20-31, 2004.

- [7] X.W. Shih and Y.W. Chang, "Fast Timing-Model Independent Buffered Clock-Tree Synthesis", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 31, No. 9, pp. 1393-1404, 2012.

- [8] R. Islam, H. Fahmy, P.Y. Lin and M.R. Guthaus, "Differential Current-Mode Clock Distribution", *Proceedings of Midwest Symposium on Circuits and Systems*, pp. 1-4, 2015.

- [9] Todri Sanial and Y. Cheng, "A Research of 3-D Power Delivery Networks with Multiple Clock Domains", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 24, No. 11, pp. 3218-3231, 2016.

- [10] M. Aguirre Hernandez and M. Linares Aranda, "CMOS Full-Adders for Energy-Efficient Arithmetic Applications", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 19, No. 4, pp. 718-721, 2011.

- [11] S. Goel, A. Kumar and M. Bayoumi, "Design of Robust, Energy Efficient Full Adders for Deep-Submicrometer Design using Hybrid-CMOS Logic Style", *IEEE Transactions on Very Large Scale Integration (VLSI)* Systems, Vol. 14, No. 12, pp. 1309-1321, 2006.