# PERFORMANCE ANALYSIS OF MEMRISTOR-BASED LOW POWER COMPUTATIONAL UNIT FOR HIGH SPEED PROCESSORS AND ITS FPGA MODELING USING FUZZY ASSISTANCE

#### **B.** Premalatha

Department of Electronics and Communication Engineering, Coimbatore Institute of Technology, India

#### Abstract

Random-access memory (RAM), however volatile, is used in modern computing systems for high-speed data transport. Memristors are employed as storage instead of solid-state devices due to their nonvolatility and lower energy needs. Memristor-based digital design has gained popularity for low-power, space-efficient VLSI design. The most important computational units for building high-speed processors is the arithmetic logic unit (ALU). Being aware that these processors' space and time requirements are significant due to the ALU's constraint, memristors are employed to get around these restrictions. Memristors are used in the design and simulation of the building components that make up an ALU. In addition to having a smaller footprint than others and reduced latency, it is a strong contender for ALU design. This work compares CMOS logic with an ALU's performance in terms of average power and integral energy for all of the memristor-based ALU's computational units. In this work, performance analysis of a memristor-based ALU has been carried out for high-speed processors, taking fuzzy metrics into account to characterise the behaviour uncertainty of the memristor. To offer a complete picture of the ALU's performance under various circumstances, fuzzy logic is utilised to evaluate the average power and integral energy of the ALU. The reconfigurable FPGAs' highlikelihood characteristics can be used to model memristors.

Keywords:

Low power VLSI circuits, Memristors, Nonvolatile Memory, Fuzzy Modeling, Field Programmable Gate Array

### **1. INTRODUCTION**

After the resistor, capacitor, and inductor, the memristor serves as the fourth crucial component in two-terminal circuits. It was first proposed by Leon Ong Chua in 1971. Its resistance can be preset (using the resistor function) and then saved (using the memory function) in a memristor, which combines memory with a resistor. Memristors are stable and maintain their state even if the device is turned off, in contrast to other types of memory used in modern electronics. But it took over 40 years until the first useful device was made. A team at HP Research Labs led by Stanley Williams revealed in 2008 that Leon Chua's memristor behaviour could be displayed in metal-oxide thin-film devices by varying the resistance between a conducting and less conducting state. Recently, memristor devices have been able to realise ultrahigh density crossbar arrays, including multiple layer stacking, with scalability down to 2-10 nm as well as very high levels of endurance and retention. Memristors have many advantages that appeal to computer scientists; including the fact that they are faster than current solid-state storage technologies and that they can store at least twice as much data in the same amount of space. They also require less energy to perform any function. Radiation has essentially no impact on memristors, whereas transistor-based technologies may experience issues.

Additionally, memristors might allow for the same style on/off switching of computers as a light switch. The arithmetic logic unit (ALU) is one of the most crucial components of high-speed processors. In order to design advanced processors that are also tiny, it is vital to decrease the amount of area that the ALU occupies on the chip. By utilising components like memristors, which are reliable and can be constructed in compact places, the need for denser integrated circuits may also be met. The current study examines the integration of fuzzy concepts into a memristor-based ALU for high-speed processors in light of the inherent uncertainty in memristor behavior. Fuzzy logic is used to replicate the resistance and storage capacity of memristors, allowing for a more complex analysis of logical and arithmetic operations within the ALU, such as AND, OR, EXOR, NAND, and NOR, as well as addition and subtraction. By using fuzzy concepts, this research aims to enhance our understanding of memristor-based ALUs.

This will help us better understand how flexible memristors are in high speed processors across a variety of scenarios and will also help us create more dependable and efficient computing systems. Recent research has focused on an ALU with a memristor-based foundation. In this work, addition and subtraction are the only arithmetic operations, and the logical operations AND, OR, EXOR, NAND, and NOR are implemented inside ALU. This study is organised around (i) designing and simulating the fundamental building blocks of an ALU-based on memristors, (ii) comparing the results of these computations with the CMOS model, and (iii) switching out transistors for memristors. Calculating power and energy is step (iv).

## 2. RELATED WORKS

Binary MRL and complementary metal oxide semiconductor (CMOS) logic elements are joined in [1] to form the fundamental elements of an arithmetic logic unit (ALU). LTSpice is used to simulate the proposed 1-bit ALU, allowing parameterization in accordance with the chosen model. This paper discussed about the effective cascadable 1-bit ALU with a voltage-level-based binary logic state through simulation. The proposed circuit performs better than benchmark circuits in terms of latency and transistor count. The authors of [2] talked about creating and demonstrating a behavioural SPICE memristor model for LTSpice's implementation of digital logic. The LTSpice model is used to simulate three different types of memristor digital logic circuits, and the results show the benefits of utilising the behavioural memristor model when designing digital systems. The writers of this article [3] go over the modular design of a CMOS and memristor-based arithmetic logic unit. The idea was put into practise using a threshold adaptive memristor model (TEAM). Functionality is checked by simulations on the Cadence Virtuoso

tool. The suggested method significantly reduces the number of transistors, which significantly reduces the overall implementation area. By comparing this approach, we can reduce chip space and power consumption while maintaining dependability. In [4], a novel hyperchaotic circuit is presented, where memristor feedback is introduced and carried out dynamically in a straightforward Lorenz-like chaotic system. Analogue circuits are used to implement the symmetrical coexistent attractors' suggested circuit, which is also studied. To demonstrate the consistency of simulation results, theoretical outcomes are contrasted.

A thorough conduction mechanism to comprehend the nonlinearity of the pure device's potentiation and depression has been put forward in [5]. The design of AND, OR, and exclusive-OR (XOR) gates utilising memristors was covered in the paper [6]. These gates have been proposed for a complete adder circuitbased on memristors. The simulation results of the proposed circuit, including all of the aforementioned gates, have been published. The proposed circuit has a significant reduction in power consumption (54.74%), delay (14.84%), and transistor count compared to the conventional circuit. The construction of combinatorial circuits utilising memristors and CMOS logic was examined, as were the characteristics of memristors. Also incorporated are built-in self-test circuits to test the fundamental logic functions [7]. By using memristor-based memory design (SRAM), [8] demonstrated the high potential property of memristors and their storage property and obtained a higher restoration yield and twice as much storage energy reduction in the proposed study. [9] looked at the anti-synchronisation of FMCC with time delay using an impulsive control approach. A few numerical instances were tested, and the stable zone was explained to demonstrate the validity of the theoretical approach.

[10] described a hybrid circuit with a memristor, meminductor, and memcapacitor connected in series. The circuit has been mathematically modelled with the aid of state equations. In DSP, the circuit was implemented, and the outcomes were discussed.[11] surveys research on low-power VLSI using gate diffusion input logic and multi-threshold voltage logic (MVT), in addition to studies relating to memristors. The solutions are suggested and simulated using common CMOS technology, with the goal of minimising energy use with less area. Results about increases in energy savings (92%) were displayed. The authors of [12] went into great length about memristors and also provided some examples of actual applications. By altering an existing model and charting it with LTSpice, the memristor is modelled. Memristors have clearly shown a lot of promise and have the potential to be yet another step in the advancement of technology towards superiority. Different complete adders with varying numbers of transistors are described in [13] and [14], and the results of their simulations are analysed.

In [15], a variety of computational logic units were designed using hybrid memristor and CMOS logic families, and experiments were conducted to illustrate the benefits of memristor features. Memristor and spin-transfer torque (STT)-RAM are two new (ReRAM) technologies that were studied by the authors of [16]. MATLAB was used for the experimentation, and the findings showed power savings of around 87% and 77%, respectively. In [17], the authors presented mFPGA, a unique CMOS-memristor hybrid reconfigurable architecture made out of CMOS-fabricated 1TIM-like components. The improvement in terms of area reduction and low power was guaranteed by the simulation findings.

Implemented a novel approach for multi-level memories, and novel CMOS-memristor-based ALUs have been presented in [18] to conceptually support this. Memristor-based ternary logic has been introduced in contrast to binary logic computing, and all the fundamental computational components have been developed. The authors in [19] implemented ternary logic and factors such as low power dissipation, chip space, component count, dense fabrication, and cost with the aid of SPICE simulation results. In order to restore signal integrity, [20] focuses on designing MRLbased gates to eliminate signal deterioration. The number of transistors, memristor cells, low power, and energy are all improving, according to simulation data. presented a novel SRAM memory cell-compatible inverter circuit-based on CMOS memristors in [21].

Memory cell experiments and analysis were done using the HSPICE software. [22] provides a thorough explanation of the memristor and its circuits. LTSPICE simulation has been used to examine the behaviour of memristors, which is appropriate for implementation in analogue circuits. [23]-[25], [28]-[30] explored the physical features of different types of memristor models.

[27] describes a memristor-based memory design. The authors of [28] discussed the number of transistors needed for various full adders that already exist and offered XOR and XNOR topologies for the 14T full adder circuit. Using the Tanner software tool, experiments were run, and their power consumption and latency were assessed. In [31], the fourth crucial component in circuit design was covered.

# 3. VOLTAGE CONTROLLED MEMRISTOR DEVICE MODELING AND ITS I-V CHARACTERISTICS

In contrast to an electrical resistor, which has a constant resistance, a memristor is a variable resistance device, meaning that the resistance value changes depending on the voltage supplied to it. A material cannot act as a memristor unless it has the reversible capacity to change its resistance in relation to the applied input voltage. Memristors are rather straightforward from a design standpoint; frequently, all they are made of is a titanium dioxide layer sandwiched between two metal electrodes. Memristor behaviour can also be seen in a few chemical compounds, including metal oxides, chalcogenides, amorphous silicon, carbon, and composite materials made of polymers and nanoparticles. They even demonstrated that it is possible to build bipolar nanodevices with memristive functionality using natural biomaterials like proteins. Researchers have also demonstrated that optical approaches, which can be taken to imply light, can be used to control the learning features of memristors in a reversible manner. As a result, scientists are hoping that memristors can be used to build electronic synapses for neuromorphic computing. These types of computing make an effort to mimic some of the learning and processing that take place in human brains. Memristive devices are first introduced using symmetry considerations, and their symbol is illustrated in Figure 1. Its I-V characteristic simulates memory operation by taking the shape of a hysteresis loop, which maintains its past state independent of the voltage applied before. The difference between a memristor and resistive memory elements is that a memristor has two terminals and is bipolar, as indicated by the black line in Fig.1.

Fig.1. Symbol for Memristor

The resistance of the gadget increases as current flows out and decreases as current enters. There are numerous models available for mapping the behaviour of memristors, and memristor modelling has been a popular area of research. Among them, voltage-controlled memristor models are widely used in memristive logic circuits known as memristor ratioed logic (MRL), which replicate memristor switching dependent on the amount of current or voltage delivered to them. In this work, we propose a fuzzy-aided technique to model voltage-controlled memristor devices and analyse their I-V properties.

Fuzzy logic can be used to better comprehend how the memristor reacts to shifting voltage inputs while taking into account the uncertainties and variances that are inherent to the behaviour of the device. Given the complexity and nonlinearity of memristors, it is hoped that the use of fuzzy concepts will provide a more accurate description of the I-V properties under ambiguous circumstances. The device modelling is more accurate thanks to the fuzzy-aided method, which also sheds light on the variations in memristor responses brought on by variations in the manufacturing process, environmental factors, and other unknowns.

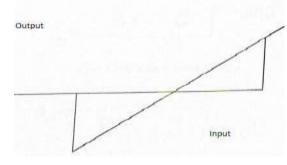

They demonstrate that the suggested fuzzy-aided method effectively captures the nuances of voltage controlled memristor behaviour through lengthy simulations and side-by-side comparisons with conventional, non-fuzzy models. This study advances our knowledge of memristor technology and lays the road for a more robust and practical integration in a variety of electronic applications. A pinched graph, like a hysteresis loop, is produced when the memristor model is simulated in LTSpice with the proper settings is shown in Fig.2.

Fig.2. Hysteresis loop of Memristor

The memristor is said to be in its "on" state when its resistance is at its lowest within the input voltage's threshold range. The term "off" refers to the memristor's extremely high resistance when it is operating outside of this range. The proposed ALU accomplishes these features using a number of building blocks, including multiplexers and logic blocks.

# 4. COMPUTATIONAL UNIT (ALU) FOR HIGH-SPEED PROCESSORS

ALUs, or fundamental computational units, are employed by high-speed processors to perform arithmetic and logical operations. Its potential to perform complicated processes comes at an increased cost, an expanded surface area, and an increase in heat and power output. Low power ALUs are in high demand in the VLSI industry as a solution to this problem. All necessary computations are performed by the arithmetic logic unit, and the majority of these procedures have logical justifications. Depending on how it is constructed, the ALU might enhance CPU performance, but this enhancement might come at the cost of increased energy consumption as well as increased heat and power generation.

In order to account for operational and performance errors, fuzzy principles are utilized in the design and analysis of the Computational Unit (ALU) for high-speed processors. By using fuzzy logic, it is possible to evaluate the ALU's performance under uncertain situations like changing input parameters or irregular computation timing.

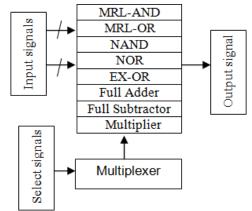

With the help of fuzzy concepts, we hope to increase the ALU's adaptability and dependability, which will eventually result in quicker, more potent processors that can handle the complexities and uncertainties of the real world. With the aid of a fuzzyaided method, the performance of the ALU in various situations can be better understood, making it an essential tool for contemporary processor design. As a result, a compromise needs to be established between the unit's overall cost and the ALU's power and complexity. The functions carried out by the ALU can generally be divided into two categories: (i) Logical Operations: These include NOR, NOT, AND, NAND, OR, XOR, and other logical operations. (ii) Bit-Shifting Operations: These operations involve moving logical bits a specific number of locations to the right or left. Addition, subtraction, multiplication, and division are included in the category of arithmetic operations as shown in Fig.3.

Fig.3. Proposed memristor-based ALU Architecture

### 4.1 MEMORY RATIOED LOGIC (MRL)-BASED OR/AND GATE DESIGN

A review of the literature revealed that memristors are an excellent choice for the modelling of a variety of logic gate designs, which are then implemented in digital computer systems B PREMALATHA: PERFORMANCE ANALYSIS OF MEMRISTOR BASED LOW POWER COMPUTATIONAL UNIT FOR HIGH SPEED PROCESSORS AND ITS FPGA MODELING USING FUZZY ASSISTANCE

because of their smaller size and faster response time. The most often used logic gates are those that depend on voltage or resistance. In Memory Ratioed Logic (MRL), OR and AND gates are designed using fuzzy concepts to account for performance variations and uncertainty. By simulating the impact of varying input signal intensities and noise on the gate's output, fuzzy logic can be used to analyse the gate's performance under uncertainty more precisely. greater dependability.

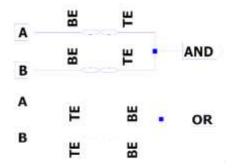

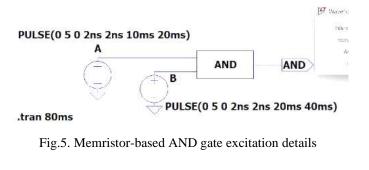

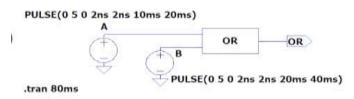

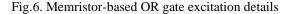

The AND and OR logic gates (MRL) are implemented using Memristor Ratioed Logic and employ voltage threshold logic as opposed to resistance threshold logic.Two binary inputs are accepted by the logic gates, with high voltage being read as logic "1" and low voltage as logic "0." The output also has a logic state that complies with the voltage. In the proposed paradigm, logic '1' is represented by 1.8 volts, whereas logic '0' is represented by 0 volts.Fig.4 depicts the memristor circuit for AND and OR logic gates. Applying a 5-volt input pulse in the manner seen in Fig.5 and Fig.6 allowed researchers to observe the properties of a memristor-based AND and OR gate. Below are the simulation results for the circuit depicted in Fig.5 and Fig.6. The node 'and' in the block denotes the output of the MRL AND gate, while the node 'or' denotes the output of the MRL OR gate. The Fig.7 and Fig.8 depicts the simulation result of the same.

Fig.4. Memristor-based (a) AND and (b) OR gates

Fig.7. Output for Memristor-based AND gate

Fig.8. Output for Memristor-based OR gate

# 5. DESIGN OF MEMRISTOR-BASED PROPOSED ALU BUILDING BLOCKS AND ITS SIMULATION RESULTS

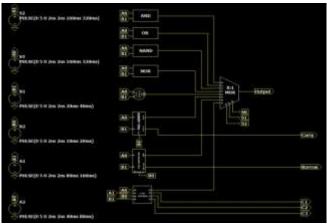

In this part, a modular ALU architecture will be discussed. The ALU is in charge of performing mathematical and logical computations. An 8:1 multiplexer is utilised in order to select one of the eight viable procedures. The 1-bit ALU is composed of the arithmetic and logical units, the 8:1 multiplexer, and other components.

#### 5.1 COMPUTATIONAL UNITS

A logical operation is a particular symbol or term that describes the linking of two or more pieces of information. It is most frequently used to establish whether a particular link between the terms is TRUE or FALSE. Several basic logic processes are covered, each of which can produce a single output value that is either TRUE (1) or FALSE (0) and receive an input value of either TRUE (1) or FALSE (0). This proposed model uses five of these seven logic operators and is described as follows: The operations needed to create the fundamental parts of an ALU, in addition to AND & OR logic gates are covered below:

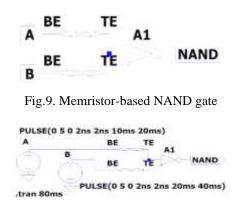

#### 5.2 MEMRISTOR-BASED NAND GATE

NAND flash is a form of flash memory that is-based on NAND logic gates, one of the universal logic gates. In Boolean algebra, the NAND value of two inputs, A and B, can be written as (A.B.)'. The Fig.9Fig.11 display the memristor-based NAND gate circuit's input and output characteristics. Fuzzy logic can be used to represent the changing resistance, capacitance, and switching characteristics of memristors, enabling a more detailed investigation of the ALU's performance under complex operating conditions. Given the complexity and non-linearity of memristors, we anticipate that by including fuzzy concepts, we will be able to increase the precision of the ALU's simulation results and better understand how they affect the ALU's operation.

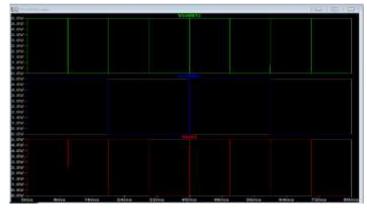

Fig.10. Memristor-based NAND gate excitation

Fig.11. Simulation output of Memristor-based NAND gate

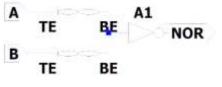

## 5.3 MEMRISTOR-BASED NOR GATE

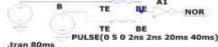

One of the two "universal" logic gates is thought to be the NOR logic gate. This is because all other logic operations may be deduced solely from NOR gates. The other variety of global logic gate is the NAND gate. The Fig.12 to Fig.14 depict the memristorbased NOR gate circuit, its symbol, and its input and output characteristics.

Fig.12. Memristor-based NOR gate

PULSE(0 5 0 2ns 2ns 10ms 20ms) A

Fig.13. Memristor-based NOR Gate excitation details

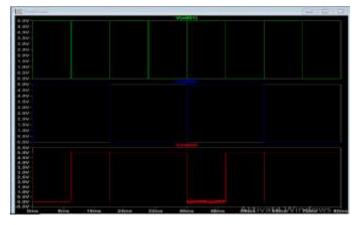

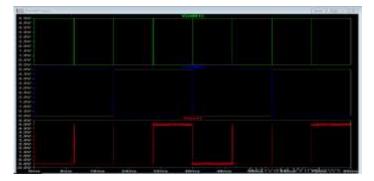

Fig.14. Memristor-based NOR Gate Output

## 5.4 MEMRISTOR-BASED XOR GATE

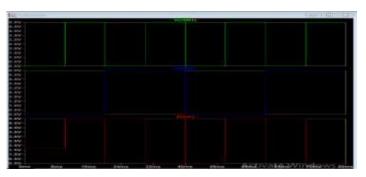

The "exclusive OR" logic operation, sometimes known as "XOR," will produce a false result if all of the inputs are identical, but a correct result if at least one of the inputs is different. The Fig.15 to Fig.17 depict an XOR gate built on a Memristor The "exclusive OR" logic operation, sometimes known as "XOR," will produce a false result if all of the inputs are identical, but a correct result if at least one of the inputs is different. The Fig.15 to Fig.17 depict an XOR gate built on a Memristor, together with its symbol, input, and output features.

Fig.15. Memristor-based XOR gate

Fig.16. Memristor-based XOR gate excitation

Fig.17. Memristor-based XOR gate output

B PREMALATHA: PERFORMANCE ANALYSIS OF MEMRISTOR BASED LOW POWER COMPUTATIONAL UNIT FOR HIGH SPEED PROCESSORS AND ITS FPGA MODELING USING FUZZY ASSISTANCE

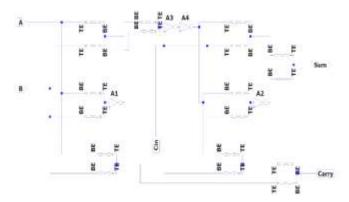

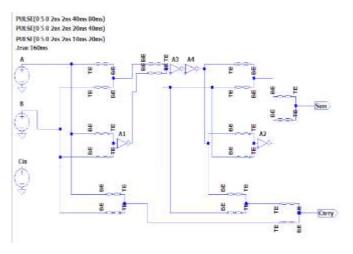

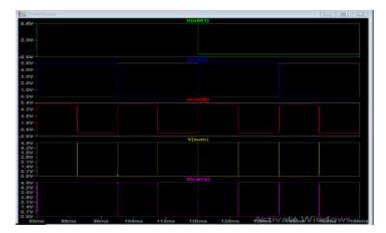

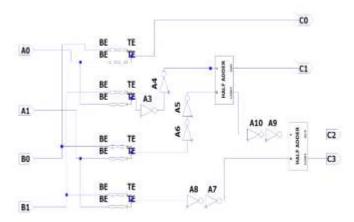

#### 5.5 MEMRISTOR-BASED FULL ADDER CIRCUIT

Memristors are used to construct the internal circuit components of full adder circuits. Two memristor-based XOR circuits are coupled with one AND gate each to make a half adder. The Fig.18 to Fig.20 display the complete memristor-based full adder circuit, together with its excitation details and output properties. In order to account for the inherent uncertainties and variability of memristors, fuzzy concepts are included in the design of a Full Adder circuit that utilises them. Fuzzy logic is used to model the nonidealities in memristor behaviour, such as fluctuations in resistance, switching thresholds, and duration, in order to better analyse the Full Adder's performance in the face of uncertainity. Because memristor devices are inherently inaccurate, we believe that by using fuzzy principles, we may strengthen and improve the Full Adder circuit while also learning more about how it responds to different inputs. The fuzzy-aided design paves the way for more robust and versatile computing units in cutting edge digital systems by highlighting the flexibility and effectiveness of the Full Adder.

Fig.18. Memristor-based Full adder circuit

Fig.19. Memristor-based Full adder circuit excitation details

Fig.20. Memristor-based Full adder output

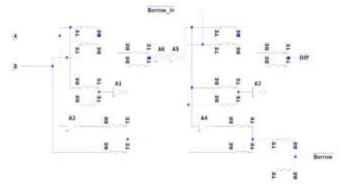

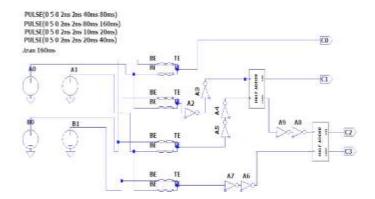

### 5.6 MEMRISTOR-BASED FULL SUBTRACTOR CIRCUIT

A full subtractor is a combinational circuit that uses three bits to accomplish subtraction. A (minuend), B (subtrahend), and Bin (borrow-in) are the names given to these bits, respectively. The letters A (minuend), B (subtrahend), and Bin (borrow bit) stand for the three input parameters, and D (difference) and Borrow (borrow out) stand for the two output outcomes. The Fig.21 to 23 depict a full subtractor circuit-based on a memristor, together with its symbol and output characteristics.

In order to account for the inherent uncertainties and fluctuations in memristor properties, fuzzy logic is used in the design of a Full Subtractor circuit that incorporates memristors. Fuzzy logic is used to represent non-linear memristor behaviour, allowing for a more detailed analysis of the Full Subtractor's performance under uncertain circumstances by taking into consideration factors like switching characteristics and resistance fluctuation. Because memristor devices are inaccurate, they want to increase the circuit's robustness by using fuzzy concepts and better understanding how the circuit behaves in various input scenarios. For the development of resilient and malleable computing units in today's cutting-edge electronic systems, fuzzy-aided Full Subtractor design is essential.

Fig.21. Memristor-based Full subtractor circuit

Fig.22. Memristor-based Full subtractor excitation details

Fig.23. Memristor-based Full subtractor output

### 5.7 MEMRISTOR-BASED 2-BIT MULTIPLIER

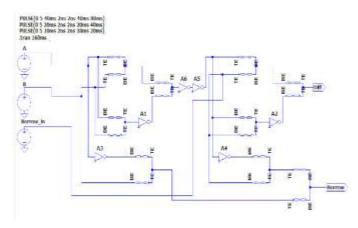

The method for multiplying two binary values is quite similar to the standard method for multiplying decimal numbers. In this method, partial products are calculated, those products are shifted, and all of the shifted products are then added. This method is quite similar to the method used to multiply two binary integers. The act of multiplying long multiplicands by 0 or 1 is much simpler than multiplying decimal numbers since the outcome of multiplying by 0 or 1 is either 0 or the same value. Fuzzy concepts are used in the design of a memristor-based 2-bit multiplier to account for uncertainties and variations in memristor characteristics.

Fuzzy logic is utilised to characterise the nonidealities in memristor behaviour, such as resistance variations and switching thresholds, in order to further analyse the multiplier's performance in confusing circumstances. Because memristor devices are inherently inaccurate, researchers believe that by utilising fuzzy notions, we may strengthen the multiplier's robustness and learn more about how it responds to different inputs. The knowledge gained from building a fuzzy-aided 2-bit multiplier allows us to improve the stability and reliability of computational units in advanced digital systems.

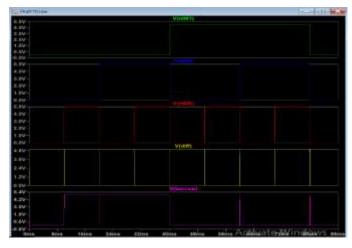

The Fig.24 is a schematic for a 2-bit binary multiplier, which is shown below. A 4-bit output with the following format is produced by multiplying the two values A1A0 and B1B0 together: C3C2C1C0. The Fig.25 represents the output of 2-bit binary multiplier.

Fig.24. Memristor-based 2-bit multiplier circuit

Fig.25. Memristor-based 2-bit multiplier excitation details

Fig.26. Memristor-based 2-bit multiplier output

#### 5.8 MEMRISTOR-BASED ALU

Memristors are employed in this design to create the fundamental components of an ALU. Addition (+), subtraction (-), multiplication (\*), and division (\*\*) are the circuit operations. Figure 30 depicts the ALU's schematic.

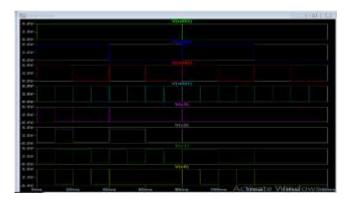

The Fig.27 illustrates how an 8:1 MUX is used in the ALU to allow for eight inputs and a single output. The Fig.28 represents the output of memristor-based ALU. The AND logic operation that is described in Table.1 is enabled by this, giving rise to I0. The logical circuit receives inputs from both A0 and B1, which

finally causes the output to undergo the AND operation. Similar to this, the selection lines S2, S1, and S0 are assigned the states 1, 0, and 1, respectively. This activates the I5 or adder circuit, which generates carry-out independently while also producing the SUM of A0, B1, and B0, which is the carry-in input, at the output of the ALU. The logical AND and complete adder circuits are chosen-based on the selection lines, and Fig.32 displays the relevant outputs. This work designs CMOS-based logic circuits and does power analysis to demonstrate the significance of memristor-based design. With proper excitation and output details various CMOS-based circuits are designed and simulated. Despite the fact that CMOS-based designs are intended for low-power VLSI designs, a power comparison with memristors has been conducted to demonstrate their performance.

Table.1. Operation Selection Table for the ALU

| Selection lines |           | Output | Ormeration |                  |  |

|-----------------|-----------|--------|------------|------------------|--|

| <b>S0</b>       | <b>S1</b> | S2     | Y          | Operation        |  |

| 0               | 0         | 0      | IO         | AND              |  |

| 0               | 0         | 1      | I1         | OR               |  |

| 0               | 1         | 0      | I2         | NAND             |  |

| 0               | 1         | 1      | I3         | NOR              |  |

| 1               | 0         | 0      | I4         | XOR              |  |

| 1               | 0         | 1      | I5         | Full Adder       |  |

| 1               | 1         | 0      | I6         | Full Subtractor  |  |

| 1               | 1         | 1      | I7         | 2-Bit Multiplier |  |

Fig.27. Memristor-based ALU circuit diagram

Fig.28. Memristor-based ALU output

# 6. POWER ANALYSIS

Various logic gates were tested using the LTSPICE software; the average power and integral energy figures are shown and reported in Table.2.

It is evident from the simulation findings that memristor-based solutions outperform CMOS-based designs in terms of average power consumption and integral energy values. As a result, ALUs created in the VLSI domain employing these circuits were assured to be low power and small in size. A computer unit's power analysis uses fuzzy concepts to account for uncertainties and variations in energy use. Improvement in power have been shown in Fig.28. Fuzzy logic is used to characterise the nonlinear relationship between various input elements and power consumption in order to analyse power performance under varied conditions.

| Table.2. Comparison of | f average power a | and Integral Energy |

|------------------------|-------------------|---------------------|

| between memris         | stor and CMOS-ba  | ased circuits       |

| Logic Circuits        | #1        | #2        |

|-----------------------|-----------|-----------|

| AND-Avg.Pwr           | 124.81 µW | 1.3211 mW |

| AND-Int.Energy        | 9.985 μJ  | 105.69 µJ |

| OR-Avg.Pwr            | 124.81 µW | 2.0091 mW |

| OR-Int.Energy         | 9.985 μJ  | 160.73 µJ |

| NAND-Avg.Pwr          | 124.82 µW | 2.2816 mW |

| NAND-Int.Energy       | 9.9589 µJ | 182.52 µJ |

| NOR-Avg.Pwr           | 124.81 µW | 2.9743 mW |

| NOR-Int.Energy        | 9.9848 µJ | 237.94 µJ |

| XOR-Avg.Pwr           | 1.2884 µW | 1.2884 mW |

| XOR-Int.Energy        | 103.07 µJ | 103.07 µJ |

| Full Adder-Avg.Pwr    | 686.45 μW | 1.8783 mW |

| Full Adder-Int.Energy | 54.916 µJ | 300.53 µJ |

Table.3. Percentage Improvement in average power and Integral energy between memristor and CMOS-based circuits

| Logic Circuits | #1    | #2    |

|----------------|-------|-------|

| AND            | 90.55 | 90.55 |

| OR             | 93.79 | 93.79 |

| NAND           | 94.53 | 94.54 |

| NOR            | 95.80 | 95.80 |

| XOR            | 99.90 | NI    |

| Full Adder     | 63.45 | 81.73 |

# 7. MEMRISTOR MODELLING USING FPGA

Memristors can be described as threshold-based or voltagedivider circuits. The need for low-power memristor circuits has been integrated into FPGA technology because of the benefits of reconfigurability, low power consumption, and high speed operation. The team can employ FPGA modelling to develop any intricate systems once they are finished. Memristors are modelled in FPGAs using the binary thresholding method. By accurately capturing the variations in memristor resistance and switching properties, fuzzy logic is used to build a more thorough and adaptable memristor model on the FPGA platform.

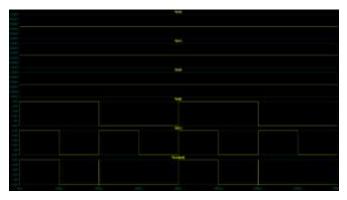

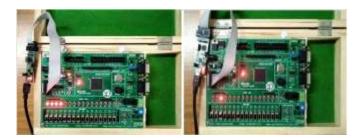

Believe that by incorporating fuzzy concepts into the simulation, we may be able to boost its fidelity given the analogue nature of memristors and their response to various voltage inputs. Fuzzy-aided modelling using an FPGA provides insights into the memristor's behaviour under ambiguous conditions, enabling more reliable and robust simulations in future VLSI design and computational research. The Xilinx Spartan 6 FPGA Kit is used to implement a few memristor-based logical processes after simulating them in HDL. Discussed are examples of HDL coding for memristor modelling, simulation findings, and hardware implementation results for memristor-based complete adder circuits.

The results of the implementation show that any complex application may be created using reconfigurable memory. The Fig.29. depict the results of experiments that were conducted using the Xilinx simulator and implemented using the Xilinx Spartan-6 FPGA XC6SLX9 kit, respectively. Discussions are had regarding memristor-based complete adder circuits and voltage divider principles and are shown in Fig.29.

Fig.29. Simulation result of memristor modelling using FPGA and its logic

Fig.30. Hardware implementation of memristor and its circuit

#### 8. CONCLUSION

The memristor, which has significantly greater potential than the typical CMOS logic transistor, is highlighted in the paper. According to the simulation results, a low-power ALU that uses memristor-based arithmetic and logic circuits has been developed that is more effective than conventional ALUs. The memristorbased logic circuit has AND, OR, NAND, NOR, and XOR gates, whereas the memristor-based arithmetic circuit has a complete adder, full subtractor, and 2-bit multiplier. A one-bit arithmetic and logic unit-based on memristors is constructed by coupling a memristor-based arithmetic circuit and a memristor-based logic circuit to an 8:1 mux. The suggested memristor-based topology maximises chip space while reducing power usage.

The developed memristor-based ALU is substantially more energy-efficient than the other ALU and uses fewer transistors than the traditional CMOS-based ALU. The introduction of fuzzy

concepts enhances memristor-based ALU design and FPGAbased memristor modelling, enabling a deeper comprehension of uncertainties and variations in memristor behaviour. Given that the fuzzy-aided technique enhances the ALU's efficiency and power optimisation, memristor-based circuits are intriguing candidates for low-power VLSI design and yield average power and total energy gains of over 90% when compared to CMOSbased circuits. The memristor, like any new technology, is commonly touted as having the potential to enhance the dependability, scalability, functionality, and energy efficiency of any conventional circuit. Although it has the potential to address a variety of problems, more effort is still required to address problems related to accurate programming and assessment of a device's state. This increases the use of memristors in the VLSI sector and is demonstrated through FPGA-based memristor modelling and its simulation outcomes.

The overall power consumption and switching properties of the proposed model are subject to further investigation. The goal of this research is to open the door for hybrid memristive circuit applications in the creation of increasingly complex computational models. Memristor-based circuits have an average power and integral energy improvement of over 90% when compared to CMOS-based circuits, indicating that they are a promising option for low-power VLSI design.

## REFERENCES

- [1] Muhammad Farhan, U. Debnath and Y. Arafat, "An Advanced 1-bit Arithmetic Logic Unit (ALU) with Hybrid Memristor-CMOS Architecture", *IEEE Transactions on Circuits and Systems I:Regular Papers*, Vol. 67, pp. 1-7, 2021.

- [2] Xiaoyuan Wang, Chenxi Jin, Jason K. Eshraghian, Herbert Ho-Chinglu and Congying Ha, "A Behavioral SPICE Model of a Binarized Memristor for Digital Logic Implementation", *Circuits, Systems, and Signal Processing*, Vol. 40, pp. 682-2693, 2021.

- [3] Ajaykumar, Bobby Kumawat and Neeta Pandey, "Design of 4-bit ALU using TEAM Memristor Model and CMOS Logic", Proceedings of International Conference on Communication and Signal Processing, pp. 28-30, 2020.

- [4] X. Wang, P. Zhou and D. Yu, "Hyperchaotic Circuit based on Memristor Feedback with Multistability and Symmetries", *Complexity*, Vol. 56, pp. 1-12, 2020.

- [5] S.Chandrasekaran, F.M. Simanjuntak, R. Saminathan, D. Panda and T.Y. Tseng, "Improving Linearity by Introducing AL in HfO2 as a Memristor Synapse Device", *Nanotechnology*, Vol. 30, No. 44, pp. 44520-44526, 2019.

- [6] M. Khalid, S. Mukhtar, M.J. Siddique and S.F. Ah- med, "Memristor based Full Adder Circuit for Better Performance", *IEEE Transactions on Electrical and Electronic Materials*, Vol. 20, pp. 403-410, 2019.

- [7] K.O. Reddy, D. Gracin, V. Ravi and S.A. Durai, "Design of Combinational Logic Circuits using Memristor and CMOS Logic", *International Journal of Innovative Technology and Exploring Engineering*, Vol. 8, pp. 167-173, 2019.

- [8] Z. Lin, Y. Wang, C. Peng, W. Lu, X. Li, X. Wu and J. Chen, "Read-Decoupled 8t1r Non-Volatile SRAM with Dual-Mode Option and High Restore Yield", *Electronics Letters*, Vol. 55, No. 9, pp. 519-521, 2019.

- [9] F. Meng, X. Zeng and Z. Wang, "Impulsive Anti-Synchronization Control for Fractional-Order Chaotic Circuit with Memristor", *Indian Journal of Physics*, Vol. 93, No. 9, pp. 1187-1194, 2019.

- [10] X. Wang, J. Yu, C. Jin, H.H.C. Iu and S. Yu, "Chaotic Oscillator based on Memcapacitor and Meminductor", *Nonlinear Dynamics*, Vol. 96, No. 1, pp. 161-173, 2019.

- [11] Kishore Sana Pala and Ramachandran Sakthivel, "Ultra Low-Voltage GDI-Based Hybrid Full Adder Design for Area and Energy-Efficient Computing Systems", *IET Circuits Devices Systems*, Vol. 13, No. 4, pp. 465-470, 2019.

- [12] J. Jayarahini and M. Udhayavani, "Modeling and Simulation of Memristor using SPICE Model", Asian Journal of Applied Science and Technology, Vol. 1, No. 2, pp. 31-35, 2017.

- [13] Priya Agrawal, D.K. Raghuvanshi and M.K. Gupta, "A Low-Power High-Speed 16T 1-Bit Hybrid Full Adder", Proceedings of International Conference on Recent Innovations in Signal Processing and Embedded Systems, pp. 27-29, 2017.

- [14] Sushant Kumar Pattnaik and Soumya R. Mohapatra, "Design and Implementation of Different Types of Full Adders in ALU and Leakage Minimization", *Proceedings of International Conference on Trends in Electronics and Informatics*, pp. 1-13, 2017.

- [15] M. Teimoori, A. Ahmadi, S. Alirezaee and M. Ahmadi, "A Novel Hybrid CMOS-Memristor Logic Circuit using Memristor Ratioed Logic", *Proceedings of IEEE Canadian Conference on Electrical and Computer Engineering*, pp. 1-5, 2016.

- [16] Yasmin Halawani, Baker Mohammad, Dirar Hom- ouz, Mahmoud Al-Qutayri and Hani Saleh, "Modeling and Optimization of Memristor and STT-RAM-Based Memory for Low-Power Applications", *IEEE Transactions on Very Large Scale Integration Systems*, Vol. 24, No. 3, pp. 1003-1014, 2016.

- [17] W.Wang, T.T. Jing and B.Butcher, "FPGA based on Integration of Memristors and CMOS Devices", *Proceedings of IEEE International Symposium on Circuits and Systems*, pp. 963-966, 2010.

- [18] C. Vourkas and G.C. Sirakoulis, "High-Radix Arithmetic-Logic Unit (ALU) Based on Memristors", Springer, 2016.

- [19] M. Khalid and J. Singh, "Memristor based Unbalanced Ternary Logic Gates", Analog Integrated Circuits and Signal Processing, Vol. 87, No. 3, pp. 399-406, 2016.

- [20] B. Liu, Y. Wang, Z. You, Y. Han and X. Li, "A Signal Degradation Reduction Method for Memristor Ratioed logic

(MRL) Gates", *IEICE Electronics Express*, Vol. 12, No. 8, pp. 20150062-20150062, 2015.

- [21] B. Abdoli, A. Amirsoleimani, J. Shamsi, K. Mohammadi and A. Ahmadi, "A Novel CMOS-Memristor based Inverter Circuit Design", *Proceedings of Iranian Conference on Electrical Engineering*, pp. 371-276, 2014.

- [22] Amisha A. Mestry, Pravin U. Dere, Sanjay M.Hundiwale and Kirti S. Agashe, "Implementation of Memristor Circuits using LTspice", *International Research Journal of Management Science and Technology*, Vol. 5, No. 8, pp. 61-69, 2014.

- [23] S. Kvatinsky, D. Belousov, S. Liman, G. Satat and N. Wald, "Magic-Memristor- Aided Logic", *IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol. 61, No. 11, pp. 895-899, 2014.

- [24] Ascoli A. Tetzlaff, R. Corinto and F. Gilli, "PSpice Switch-Based Versatile Memristor Model", *Proceedings of IEEE International Symposium on Circuits and Systems*, pp .205-208, 2013.

- [25] S. Kvatinsky, E.G. Friedman, A. Kolodny and U.C. Weiser, "Team: Threshold Adaptive Memristor Model", *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 60, No. 1, pp. 211-221,2013.

- [26] S.S. Sarwar, S.A.N. Saqueb, F. Quaiyum and A.B.M.H.U. Rashid, "Memristor-Based Nonvolatile Random Access Memory: Hybrid Architecture for Low Power Compact Memory Design", *IEEE Access*, Vol. 1, pp .29-34, 2013.

- [27] P.T. Vanathi, J. Ramesh, K. Revathy, R. Preethi, C. Haritha Laxmi and K. Keerthana, "Performance Analysis of High-Performance Adder Architectures", *Bonfring International Journal of Power Systems and Integrated Circuits*, Vol. 2, No. 1, pp. 1-7, 2012.

- [28] M. Mahvash and A.C. Parker, "A Memristor SPICE Model for Designing Memristor Circuits", *Proceedings of IEEE International Midwest Symposium on Circuits and Systems*, pp. 989-992, 2010.

- [29] S. Benderli and T.A. Wey, "On SPICE Macromodelling of TiO2 Memristors", *IET Electronics Letters*, Vol. 45, No. 7, pp. 377-379, 2009.

- [30] Z. Biolek, D. Bioleka and V. Biolkova, "SPICE Model of Memristor with Nonlinear Dopant Drift", *Radio Engineering*, Vol. 18, No. 2, pp. 210-214, 2009.

- [31] D.B. Strukov, G.S. Snider, D.R. Stewart and R.S. Williams, "The Missing Memristor Found", *Nature*, Vol. 453, pp. 80-83, 2008.