## EFFECT OF ADDER CIRCUITS OVER MULTIPLIER DESIGN BASED ON VEDIC MATHEMATICS

### Saurabh Singh and Sunita Soni

Department of Computer Science and Engineering, Bhilai Institute of Technology, India

#### Abstract

Multiplication is critical for computers linked to cryptography or the ALU function. It consumes more chip area and time than the other ALU functions. The speed of the processor, coprocessor, or embedded system may depend on the multipliers' speed. Nowadays, designing a small, high-performance multiplier is a critical challenge in computer architecture, cryptographic hardware design, and embedded system design. One of the better solutions is developing a digital multiplier design based on Vedic mathematical formula. The performance of the Digital Vedic Multiplier (DVM) is entirely dependent on the adder network. DVM is evaluated here using KS Adder and CLA Adder. There are several publications on this topic, but the primary shortcoming is that they focus exclusively on the DVM without addressing the influence of the adder circuit. This work aims to investigate the impact of the adder circuit on the space-speed trade-off inherent in the design of the DVM.

Keywords:

Vedic Mathematics, Digital Vedic Multiplier, Adder, Urdhv Triyagyabhyam, Speed

### **1. INTRODUCTION**

Arithmetic operations are essential for the architecture of digital processors and application-specific systems. Multipliers are essential components of a wide range of high-efficiency systems, including FIR, microcontrollers, microprocessors, embedded processor digital signal processors (DSP), and other types of computer circuits. Because the multiplier is typically the slowest subsystem of any processing system, the efficiency of a system is typically determined by the output of the multiplier, which is typically the slowest subsystem. Furthermore, it is typically the most expensive option when it comes to consuming space because of this, increasing the speed and area of the multiplier might be a substantial design issue. On the other hand, area and speed are generally conflicting constraints, with the result that speed increases occur mostly in greater areas [1]-[5], [10]-[15].

Conventional multiplication is based on three basic calculations

- Generation of the partial product (PPG)

- Reduction of Partial Product (PPR)

- Carry propagates addition (CPA)

All three steps required high logic hardware. To enhance the multiplier's performance, rearrangement of the adder is one of the old methods [16]. Vedic mathematics is ravelled by Shankaracharya Ji Barti Kirshna Teerathji Maharaj (1884-1960) from Sthaptya-Veda, Up-Veda of Atharv Veda, Shankaracharya Ji gave 16 sutras and 16 Sub sutras (Formula and subformula).

The formula suggested in Vedic mathematics is also suitable for the design figure of the digital multiplier. Multiplier based on Vedic mathematics yields higher speed than other multipliers [6]. In previous work, most researchers pay attention to speed parameters; for example, in [25]-[30], they design High-Speed ALU but silent over space requirements. So, this may lead to a choice dilemma for future researchers who have to develop a high-speed circuit with limited resources. This paper tries to find a tread-off between space and speed.

### 2. URDHV-TRIYAGYABHAYM: THE VEDIC SUTRA, VERTICAL AND CROSS

In this sutra, partial products are generated vertically and cross manner [15]. The main advantage of this formula is that it will produce all the partial products in parallel and then sum up them. For example, we considered  $12 \times 13$  (decimal multiplication of 12 and 13). This sutra includes the following steps

- Multiply 2 and 3  $(2\times3) = 6$  (vertical multiplication) (in this case, there is single-digit number 6, we can write it as 06 here 0 will be treated as carry for step 3; this step gives list significant digit of result 6 in this case.

- Multiply 1 and 1  $(1 \times 1) = 1$  (vertical multiplication) (If this step answers more digits, then the least significant of this result will be added to the outcome of step 3 as a most significant bit, and if this sum yields any carry, then this carry will be added to the remaining digit of this step, i.e., step 2; this will give us most significant digits of multiplication.

- Multiply 1 and 3 (1×3) and multiply 1 and 2 (1×2) add them with carry from step 1 and list significant bit of step 3 if any (cross multiplication); 1×3+1×2+0=5; this step gives us the middle term of the result.

- Now answer is 06+20+30+100=156 [1].

- Let's assume an example  $12 \times 13$ :

- $1 \times 1 = 1$  (100th position) (vertical multiplication) yield 100

- $2 \times 1 = 2$  (10th Position) (cross multiplication) yield 20

- $3 \times 1 = 3$  (10th Position) (cross multiplication) yield 30

- $2 \times 3 = 6$  (unit position) (vertical multiplication) yield 06

- Let's assume another example 99×99:

- 9×9=81 (vertical multiplication of most significant digit; yield 8100 (81\*100))

- 9×9=81(cross multiplication yield 81\*10=810; 10th position)

- 9×9=81(cross multiplication yield 81\*10=810; 10th position)

- 9×9=81 (vertical multiplication of least significant digit; yield 81)

So, result is (8100+810) + (810+81) = 9801.

# **3. THE MULTIPLIER (DIGITAL VEDIC MULTIPLIER (DVM))**

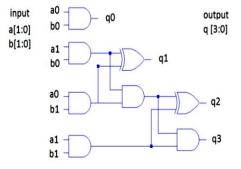

The DVM can be implemented by two sutras, namely Urdhv-Triyagbham Sutra and Nikhila Sutra [21]-[23]. The DVM can be implemented by a 2×2-bit multiplier, as shown in Fig.1 [9]. This design may also be utilized as a fundamental building element for implementing  $4\times4$ ,  $8\times8$ ,  $16\times16$ , and other multipliers [17].

Fig.1. Implementation of 2×2 bit Digital Vedic Multiplier

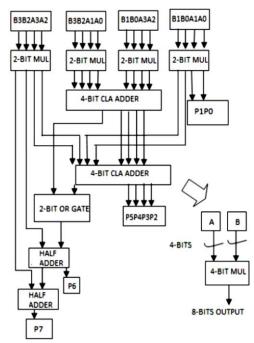

Many designs are available to implement the above sutra into a high-speed digital multiplier [18] [19]. The Fig.2 shows that this design requires four multipliers, two adders, and one-half adder network [7]. The Fig.2 is the design implementation of a 4-bit digital multiplier that needs a 2-bit multiplier [20].

When we increase the number of bits, the design in Fig.2 will lead to more delay due to the half adder network. However, this design shows a better result than the booth algorithm reported in [7].

Fig.2. Implementation of 4×4-bit Digital Vedic Multiplier

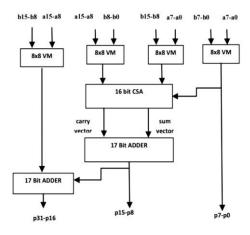

Another design of (Fig.3) 16-bit multiplier as described in [8] requires 4, 8bit multiplier and 1, 16-bit CS Adder and 2, 17-bit Adders for implementing multiplier of 16 bit.

Fig.3. Implementation of 16x16 bit Digital Vedic Multiplier

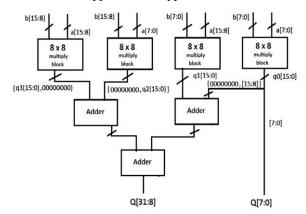

In Fig.4, the  $16 \times 16$  DVM is rendered with 4,  $8 \times 8$  blocks. Here are the bit (n=16) multiplicands, which result in a 32-bit size. For both inputs, a and b, the input is divided into smaller segments of 0.5n size. i.e. 8. The lower part (8bits) of  $q_0$  are passed directly to the result, while the upper bits are applied to the addition tree [6].

Fig.4. Implementation of 16×16 bit Digital Vedic Multiplier

The whole process can be summarized for *N* bit multiplier as follows:

Let's assume *A* and *B* are two n bit numbers divided into higher and lower order, i.e.  $A_h$ ,  $A_l$ ,  $B_h$  and  $B_l$ . Then the partial product can be generated in the following manner  $A_h A_l \times B_h B_l$ .

- Partial product  $1 A_h \times B_h$  (Vertical Product)

- Partial Product  $2 A_l \times B_l$  (Vertical Product)

- Partial Product  $3 A_h \times B_l$  (Cross Product)

- Partial Product  $4 A_l \times B_h$  (Cross Product)

To generate partial products 1, 2, 3, and 4, we need four multipliers of 0.5n bits. After generating all partial products, we must add the entire partial product to our final result. In addition, three adders will be required.

## 3.1 KEY PLAYER FOR SPEED AND AREA (ADDERS)

From the above design, it is clear that the adder plays a crucial role in the speed and performance of the digital Vedic multiplier. If we modify the configuration of the adder, then we can find the trade-off between the area and speed of the digital multiplier [11].

In [12], they used KS Adder to speed up the performance of DVM at the cost of the area. This paper examines speed and area tradeoffs for KS adder and CLA adder. The K-S adder and CLA adder design are discussed in [11].

### 4. RESULTS AND DISCUSSION

This paper implements *KS* Adder and CLA Adder for addition blocks. The output of 8-bit KSA is shown in Fig.5

|                                     |      |       |        | 0E          | 2.3   |      |      |         |         |        |       |

|-------------------------------------|------|-------|--------|-------------|-------|------|------|---------|---------|--------|-------|

| Current Simulation<br>Time: 1000 ns |      | D     | 20     | )0<br>      | 40    | 0    | 6    | 00<br>I | 81      | 00<br> | 1000  |

| 🔊 cout (                            | 0    |       |        |             |       |      |      |         |         |        |       |

| 🖬 💏 s[7:0] 🛛 🛛 8                    | 8h55 | 8'h00 | 8110   | B'h56 X 8   | h55 X | 8hDD | 8hDC | (8hDD)  | (B'hOC) | (8hDD) | B'hDC |

| o cin (                             | 0    |       | al Ar  |             |       |      |      |         |         |        |       |

| 🗉 😽 A[7:0] 🛛 🛛 🗧                    | 8h22 | 8"h00 | (8h11) | 8h22 X 8hFF |       |      |      |         |         |        |       |

| 🖬 😽 B [7:0] 🛛 🛛 8                   | 8h33 | 8'h00 | (8hFF) | 8h33        | X     |      |      | B'hl    | DD      |        |       |

Fig.5. Output of 8-bit KSA

And the output of 8-bit CLA adder is shown in Fig.6, and the output of DVM 4 bit is shown in Fig.7

| Time: 1000 ns     D     200     400     600     800       igl cout     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ime: 1000 ns D 200 400 600 800 100<br>∬ cout 0<br>₩ 5[7:0] 8 h94 (sh00 (sh10))/( sh3A (sh95 )/ sh3A (sh95))/( sh11 \ sh10 \ sh11 \ sh10<br>∬ cin 1<br>₩ 4[7:0] 8 h44 (sh00 \ shFF \ sh44 \ 8h22 |                                     | 440.1 |         |             |                     |                   |               |        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|---------|-------------|---------------------|-------------------|---------------|--------|--|

| Bits[7:0]     8h94     Sh00     X0H10     X     8h93     X     8h94     Sh10     X     8h94     Sh10     X     8h94     Sh10     X     8h93     X     8h94     Sh10     Sh11     X     8h11     X     8h11 </th <th>M 6[7:0] 8h94 (3h00 (0h10 )/ 3h04 (0h95 ) 3h24 (2h90 )/ 9h11 ( 9h10 ( 9h11 ) 9h10<br/>   cin 1<br/>   A (7:0] 8h44 (3h00 (8hFF ) 8h44 ) 8h22</th> <th>Current Simulation<br/>Time: 1000 ns</th> <th></th> <th>D</th> <th>200</th> <th>400</th> <th>600</th> <th>800</th> <th>100</th> | M 6[7:0] 8h94 (3h00 (0h10 )/ 3h04 (0h95 ) 3h24 (2h90 )/ 9h11 ( 9h10 ( 9h11 ) 9h10<br>   cin 1<br>   A (7:0] 8h44 (3h00 (8hFF ) 8h44 ) 8h22                                                      | Current Simulation<br>Time: 1000 ns |       | D       | 200         | 400                 | 600               | 800           | 100    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cin 1                                                                                                                                                                                           | of cout                             | 0     |         |             |                     |                   |               |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MA(7.0) 81144 Sh00 X8hFF X Sh44 X 81h22                                                                                                                                                         | 🖬 😽 s[7:0]                          | 8h9A  | ( 9'h00 | (8h10)(X 8' | haA 🗙 8 h 99 🗙 8 ha | A X 8'h99 X 8'h11 | X 8h10 X 8h11 | X 8510 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                 | ol cin                              | 1     |         |             | ر و الحک س          | هد أنساره         |               |        |  |

| On 44 STUD 2811F 2 STA4 2 STA2 STA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ■8[7.0] 9h55 8h00 x8h11 x 8h55 x 8hEE                                                                                                                                                           | 🖬 😽 A[7:0]                          | 81144 | 8'h00   | (8hFF)      | 8'h44               | X                 | 8'h22         |        |  |

| 846[70] 9h55 sh00 (sh11) Sh55 ( sh00 (sh11))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 | 🖬 😽 8(7:0)                          | 8h55  | 8'600   | (8h11)      | 8'h55               | X                 | 8'hEE         |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                 |                                     |       |         |             |                     |                   |               |        |  |

Fig.6. Output of 8-bit CLA Adder

|       | 740.5 |                          |                 |                                                                  |                                                            |                                                                                             |  |  |

|-------|-------|--------------------------|-----------------|------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

|       | 4     | 00                       | 600             |                                                                  | 800                                                        | 1000                                                                                        |  |  |

| 8'h1C | 8'hOF | ( 8'h00 )                | 8'h0E           | X                                                                | 8'h1C                                                      | 31                                                                                          |  |  |

| 4'hE  | 4'h1  | ( 4h0 )                  |                 |                                                                  | he                                                         |                                                                                             |  |  |

| 4'h2  | 4'hF  | X                        | 4m1             | X                                                                | 4'h2                                                       |                                                                                             |  |  |

|       |       | <u>.</u>                 |                 |                                                                  |                                                            |                                                                                             |  |  |

|       |       |                          |                 |                                                                  |                                                            |                                                                                             |  |  |

|       | 4'hE  | 8'h1C 8'h0F<br>4'hE 4'h1 | 4'hE 4'h1 X 4h0 | Shife     8h0F     8h00     8h0E       4hE     4h1     4h0     4 | 400 600<br>1 1 1<br>S'h1C 8h0F 8h00 8h0E<br>4'hE 4h1 4h0 8 | 400     600     800       Sh1C     Sh0F     Sh0E     Sh1C       4hE     4h1     4h0     ShE |  |  |

Fig.7. Output of 4-bit Digital Vedic Multiplier

| Table.1. Result | Reported in [11] |

|-----------------|------------------|

|-----------------|------------------|

| Parameter | CLA DVM   | KSA DVM    |

|-----------|-----------|------------|

| Area      | 89 Slices | 105 Slices |

| Delay     | 29.891 ns | 31.788     |

Table.2. Result of [24]

| Parameter | 4-bit RCA Adder | 4-bit KS Adder |

|-----------|-----------------|----------------|

| Area      | 23 Slices       | 19 Slices      |

| Delay     | 12.421 ns       | 11.737         |

Table.3. Result Of Adders

| Parameter | 8-bit CLA Adder | 8-bit KS Adder |

|-----------|-----------------|----------------|

| Area      | 9 Slices        | 16 Slices      |

| Delay     | 15.235 ns       | 14.005         |

Table.4. Comparison of DVM based on CLA Adder and KS Adder

| Parameter | 8-bit DVM<br>(CLA) | 8-bit DVM (KS<br>Adder) | 8 Array<br>Multiplier |

|-----------|--------------------|-------------------------|-----------------------|

| Area      | 95 Slices          | 108 Slices              | 71                    |

| Delay     | 25.269 ns          | 24.489                  | 25.527                |

From Table. 1 to Table.4, it is clear that CLA implementation of DVM consumes less hardware, 95 slices, as compared to 108 slices of KSA. However, KSA implementation gives better speed, it is tested for the 8-bit multiplier, and if we increase the number of the bit, then hardware requirement will also increase. This work helps the designer to choose a better option for their implementation.

### 5. CONCLUSION

In this paper, Digital Vedic Multiplier is designed and implemented in VHDL and compiled by the Xilinx synthesis tool (XST) [14]. The Table.1 shows the result of [11], Table.2 shows the analysis of adders and Table.3 shows the design implemented in this paper. The results clearly shows that we can optimize DVM for speed or area. This work can be extended with other available adders to find a better trade-off between area and time.

### REFERENCES

- [1] S.B.K. Tirtha and V.S. Agrawala, "Vedic Mathematics", Motilal Banarsidass Publishers Private Limited, 2013.

- [2] S. Singh, "Design of High-Speed Multiplier using Ancient Indian", Master Thesis, Department of Electronics, Chhattisgarh Swami Vivekanand Technical University, pp. 1-87, 2009.

- [3] H. Thapliyal and M.B. Srinivas, "High Speed Efficient NxN Bit Parallel Hierarchical Overlay Multiplier Architecture Based on Ancient Indian Vedic Mathematics", *Enformatika*, Vol. 2, pp. 225-228, 2004.

- [4] H. Thapliyal and H.R. Arabnia, "A Time-Area-Power Efficient Multiplier and Square Architecture Based on Ancient Indian Vedic Mathematics", *Proceedings of International Conference on Embedded Systems and Applications*, pp. 434-439, 2004.

- [5] H. Thapliyal and M.B. Srinivas, "VLSI Implementation of RSA Encryption System using Ancient Indian Vedic Mathematics", *Proceedings of International Conference on Microtechnologies for the New Millennium*, pp. 888-892, 2005.

- [6] A. Singh, "Implementation of 16 Bit Vedic Multiplier", Master Thesis, Department of Electrical and Electronics Engineering, Thapur University, pp. 1-72, 2010.

- [7] R.K. Bathija, R.S. Meena, S. Sarkar and R. Sahu, "Low Power High Speed 16x16 bit Multiplier using Vedic

Mathematics", *International Journal of Computer Applications*, Vol. 59, No. 6, pp. 41-44, 2012.

- [8] M. Pradhan, R. Panda and S.K. Sahu, "Speed Comparison of 16x16 Vedic Multipliers", *International Journal of Computer Applications*, Vol. 21, No. 6, pp. 1-14, 2011.

- [9] C. Venkatesan and P. Karthigaikumar, "An Efficient Noise Removal Technique using Modified Error Normalized LMS Algorithm", *National Academy Science Letters*, Vol. 41, No. 3, pp. 155-159, 2018.

- [10] S. Kannan, C. Selvaraj and S.N. Mohanty, "Forecasting Energy Generation in Large Photovoltaic Plants using Radial Belief Neural Network", *Sustainable Computing: Informatics and Systems*, Vol. 34, No. 2, pp. 1-17, 2021.

- [11] A.R. Suhas and M.M. Priyatham, "Heal Nodes Specification Improvement using Modified Chef Method for Group Based Detection Point Network", *International Journal of Pervasive Computing and Communications*, Vol. 33, No. 2, pp. 1-12, 2021.

- [12] M. Ramkumar, R. Manikandan, K.S. Kumar and R.K. Kumar, "Intrusion Detection in Manets using Support Vector Machine with Ant Colony Optimization", *ICTACT Journals on Data Science and Machine Learning*, Vol. 1, No. 1, pp. pp. 37-42, 2019.

- [13] Y. Bansal, C. Madhu and P. Kaur, "High Speed Vedic Multiplier Designs - A Review", *Recent Advances in Engineering and Computational Sciences*, Vol. 2014, pp. 1-6, 2014.

- [14] S. Akhter, "VHDL Implementation of Fast NxN Multiplier based on Vedic Mathematic", *Proceedings of International Conference on Circuit Theory and Design*, pp. 472-475, 2007.

- [15] R. Pushpangadan, V. Sukumaran and V. Sundar, "High Speed Vedic Multiplier for Digital Signal Processors", *IETE Journal of Research*, Vol. 55, No. 6, pp. 282-286, 2009.

- [16] A. Kanhe, S.K. Das and A.K. Singh, "Design and Implementation of Floating Point Multiplier based on Vedic Multiplication Technique", *Proceedings of International Conference on Communication, Information and Computing Technology*, pp. 1-4, 2012.

- [17] V. Kunchigik, L. Kulkarni and S. Kulkarni, "Pipelined Vedic-Array Multiplier Architecture", *International Journal* of Image, Graphics and Signal Processing, Vol. 6, No. 6, pp. 58-67, 2014.

- [18] T. Karthikeyan, K. Praghash and K.H. Reddy, "Binary Flower Pollination (BFP) Approach to Handle the Dynamic Networking Conditions to Deliver Uninterrupted Connectivity", *Wireless Personal Communications*, Vol. 121, No. 4, pp. 3383-3402, 2021.

- [19] S. Srimani, D.K. Kundu, S. Panda and B. Maji, "Implementation of High Performance Vedic Multiplier and Design of DSP Operations Using Vedic Sutra", *Proceedings* of International Conference on Computational

Advancement in Communication Circuits and Systems, pp. 443-449, 2015.

- [20] S. Srimani, D.K. Kundu, S. Panda and B. Maji, "Implementation of Optimized High Performance 4x4 Multiplier using Ancient Vedic Sutra in 45 nm Technology", *Proceedings of International Conference on Devices, Circuits and Systems*, pp. 1-6, 2014.

- [21] K.B. Jagannatha, H.S. Lakshmisagar and G.R. Bhaskar, "FPGA and ASIC Implementation of 16-Bit Vedic Multiplier Using Urdhva Triyakbhyam Sutra", Proceedings of International Conference on Emerging Research in Electronics, Computer Science and Technology, pp. 31-38, 2014.

- [22] H. Sharma, G.K. Jindal, and P.R. Murthy, "Comparison Between Array Multiplier and Vedic Multiplier", *International Journal of Electronics and Communication Engineering and* Technology, Vol. 8, No. 3, pp. 1-14, 2014.

- [23] M. Pradhan and R. Panda, "High Speed Multiplier using Nikhilam Sutra Algorithm of Vedic Mathematics", *International Journal of Electronics*, Vol. 101, No. 3, pp. 300-307, 2014.

- [24] A. Tiwari and S. Lal, "An Approach Towards the High-Efficient and low Propagation Delay in Digital Processor", *International Journal of Electrical, Electronics and Computer Engineering*, Vol. 6, No. 1, pp. 62-70, 2017.

- [25] J. Kumar, K. Selva, and R. Rahim, "Design and UVM Verification of High Speed ALU", *International Journal on Emerging Technologies*, Vol. 10, No. 1, pp. 93-96, 2019.

- [26] G.G. Kumar and V. Charishma, "Design of High Speed Vedic Multiplier using Vedic Mathematics Techniques", *International Journal of Scientific and Research Publications*, Vol. 2, No. 3, pp. 1-15, 2012.

- [27] R. Santhiya and M.T. Thamaraimanalan, "Power Gating Based Low Power 32 Bit BCD Adder using DVT", *International Journal for Scientific Research and Development*, Vol. 3, No. 2, pp. 802-805, 2015.

- [28] R.K. Kodali, S.S. Yenamachintala and L. Boppana, "FPGA Implementation of 160-Bit Vedic Multiplier", *Proceedings* of International Conference on Devices, Circuits and Communications, pp. 1-5, 2014.

- [29] C.Venkatesan, P. Karthigaikumar, A. Paul, S. Satheeskumaran and R. Kumar, "ECG Signal Preprocessing and SVM Classifier-Based Abnormality Detection in Remote Healthcare Applications", *IEEE Access*, Vol. 6, pp. 9767-9773, 2018.

- [30] K. Praghash and T. Karthikeyan, "An Investigation of Garbage Disposal Electric Vehicles (GDEVs) Integrated with Deep Neural Networking (DNN) and Intelligent Transportation System (ITS) in Smart City Management System (SCMS)", Wireless Personal Communications, Vol. 124, No. 2, pp. 1-20, 2021.